IBM is announcing a research plan to invest $3 billion over the next five years to build chips that meet the requirements of cloud computing and big data systems.

The investment is aimed at preserving IBM’s leadership role in producing the breakthroughs necessary to stay on track with Moore’s Law — the prediction by Intel chairman emeritus Gordon Moore that the number of basic components, or transistors, on a chip will double every couple of years.

Only a handful of other chip companies, such as Intel and Taiwan Semiconductor Manufacturing Co., will be able to match this kind of initiative.

The first research program to be funded under the new plan will be so-called “7 nanometer and beyond” silicon technology. IBM’s scientists will try to push the limits of silicon chips to 7 nanometers (7 billionths of a meter) and below. That figure refers to the width between electrical circuits. It is more than 1,400 times more narrow than a human hair. Such manufacturing will test the ability of chip makers to miniaturize their designs without running afoul of the laws of physics.

The first research program to be funded under the new plan will be so-called “7 nanometer and beyond” silicon technology. IBM’s scientists will try to push the limits of silicon chips to 7 nanometers (7 billionths of a meter) and below. That figure refers to the width between electrical circuits. It is more than 1,400 times more narrow than a human hair. Such manufacturing will test the ability of chip makers to miniaturize their designs without running afoul of the laws of physics.

The second program will explore alternative technologies for a post-silicon era. Silicon has been the basic material for a semiconductor chip for decades, but it is running into physical limits.

IBM needs this accelerant because cloud and big data applications are placing new challenges on systems, just as the underlying chip technology is facing numerous significant physical limits. The newest chips need dense memory, high-speed connectivity, and lower power consumption.

Big Blue will use IBM Research scientists and engineers from Albany and Yorktown, N.Y.; Almaden, Calif.; and Zurich, Switzerland. The company will hire significant new numbers of researchers in areas such as carbon nanoelectronics, silicon photonics, new memory technologies, and architectures that support quantum and cognitive computing. All of those areas are promising in terms of replacing silicon and advancing computing. The teams need a 10-fold improvement in system-level performance and energy efficiency in order to hit their goals.

IBM said it will also continue to invest in the nanosciences and quantum computing — two areas of fundamental science where IBM has done pioneering work for decades.

For the 7-nanometer-and-beyond plan, IBM will try to shrink the width between chip circuits from today’s 22 nanometers to 14 nanometers. Then it will shrink it to 10 nanometers, and eventually it will target 7 nanometers and below. To get there will require huge new innovations. During one of these transitions, silicon technology might very well hit its physical limit.

“The question is not if we will introduce 7 nanometer technology into manufacturing, but rather how, when, and at what cost,” said John Kelly, senior vice president, IBM Research, in a statement. “IBM engineers and scientists, along with our partners, are well suited for this challenge and are already working on the materials science and device engineering required to meet the demands of the emerging system requirements for cloud, big data, and cognitive systems. This new investment will ensure that we produce the necessary innovations to meet these challenges.”

“The question is not if we will introduce 7 nanometer technology into manufacturing, but rather how, when, and at what cost,” said John Kelly, senior vice president, IBM Research, in a statement. “IBM engineers and scientists, along with our partners, are well suited for this challenge and are already working on the materials science and device engineering required to meet the demands of the emerging system requirements for cloud, big data, and cognitive systems. This new investment will ensure that we produce the necessary innovations to meet these challenges.”

An outside chip expert verified the scale of the challenge ahead for IBM, which has more than 2,500 patents in this field.

“Scaling to 7nm and below is becoming a difficult challenge. This requires deep physics and nano material expertise. IBM is one of only a few companies in the world that can do this level of science and engineering,” said Richard Doherty, director of technology at Envisioneering Group, in a statement.

IBM said that there is an urgent need to develop new materials for chips and new circuit architectures, or chip designs. The current manufacturing process — complementary metal oxide semiconductor (CMOS) — has lasted for a lot longer than expected. But IBM says new alternatives could include carbon nanotubes and computational approaches such as neuromorphic computing (brain-like computers) and quantum computing. IBM said it will continue to work with other industry consortia and universities too.

Here’s how IBM describes each promising area of technology:

Quantum Computing

The most basic piece of information that a typical computer understands is a bit. Much like a light that can be switched on or off, a bit can have only one of two values: “1” or “0”. For a quantum bit or a “qubit” for short, they can hold a value of “1” or “0” as well as both values at the same time. Described as superposition, this is what allows quantum computers to perform millions of calculations at once.

The special properties of qubits will allow quantum computers to weed through millions of solutions all at once, while desktop PCs would have to consider them one at a time.

IBM is a world leader in superconducting qubit based quantum computing science and is a pioneer in the field of experimental and theoretical quantum information, fields that are still in the category of fundamental science but one that, in the long term, may allow the solution of problems that are today either impossible or impractical to solve using conventional machines. The team recently demonstrated the first experimental realization of parity check with three superconducting qubits, an essential building block for one type of quantum computer.

Neurosynaptic Computing

Bringing together nanoscience, neuroscience, and supercomputing, IBM and university partners have developed an end-to-end ecosystem including a novel non-von Neumann architecture, a new programming language, as well as applications. This novel technology allows for computing systems that emulate the brain’s computing efficiency, size and power usage. IBM’s long-term goal is to build a neurosynaptic system with ten billion neurons and hundred trillion synapses, all while consuming only one kilowatt of power and occupying less than two liters of volume.Silicon Photonics

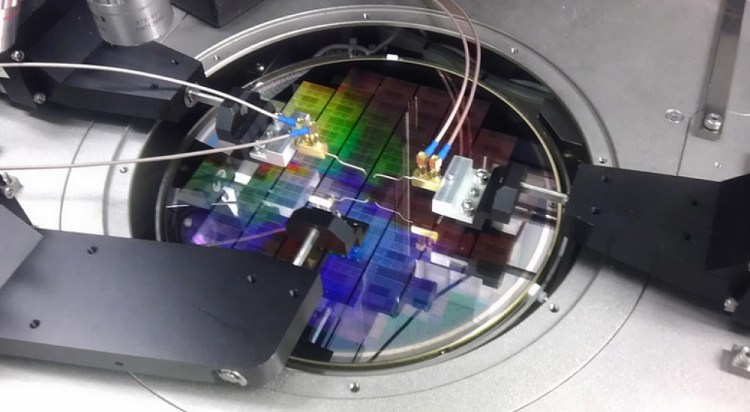

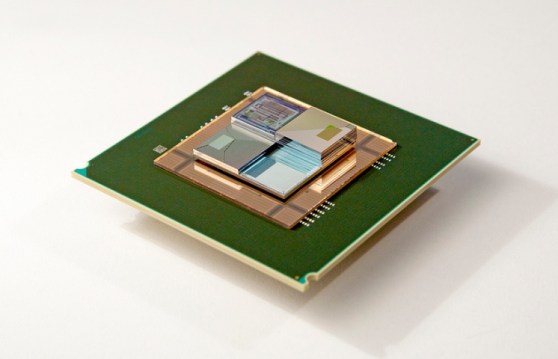

IBM has been a pioneer in the area of CMOS integrated silicon photonics for over 12 years, a technology that integrates functions for optical communications on a silicon chip, and the IBM team has recently designed and fabricated the world’s first monolithic silicon photonics based transceiver with wavelength division multiplexing. Such transceivers will use light to transmit data between different components in a computing system at high data rates, low cost, and in an energetically efficient manner.Silicon nanophotonics takes advantage of pulses of light for communication rather than traditional copper wiring and provides a super highway for large volumes of data to move at rapid speeds between computer chips in servers, large datacenters, and supercomputers, thus alleviating the limitations of congested data traffic and high-cost traditional interconnects.

Businesses are entering a new era of computing that requires systems to process and analyze, in real-time, huge volumes of information known as Big Data. Silicon nanophotonics technology provides answers to Big Data challenges by seamlessly connecting various parts of large systems, whether few centimeters or few kilometers apart from each other, and move terabytes of data via pulses of light through optical fibers.

III-V technologies

IBM researchers have demonstrated world’s highest transconductance on a self-aligned III-V channel MOSFET device structure that is compatible with CMOS scaling. These materials and structural innovation is expected to pave path for technology scaling at 7nm and beyond. With more than an order of magnitude higher electron mobility than silicon, integrating III-V materials into CMOS enables higher performance at lower power density, thus allowing for an extension to power/performance scaling to meet the demands of cloud computing and big data systems.Carbon Nanotubes

IBM Researchers are working in the area of carbon nanotube (CNT) electronics and exploring whether CNTs can replace silicon beyond the 7 nm node. As part of its activities for developing carbon nanotube based CMOS VLSI circuits, IBM recently demonstrated — for the first time in the world — 2-way CMOS NAND gates using 50 nm gate length carbon nanotube transistors.IBM also has demonstrated the capability for purifying carbon nanotubes to 99.99%, the highest (verified) purities demonstrated to date, and transistors at 10 nm channel length that show no degradation due to scaling–this is unmatched by any other material system so far.

Carbon nanotubes are single atomic sheets of carbon rolled up into a tube. The carbon nanotube forms the core of a transistor device that will work in a fashion similar to the current silicon transistor, but will be better performing. They could be used to replace the transistors in chips that power our data-crunching servers, high performing computers and ultra fast smart phones.

Carbon nanotube transistors can operate as excellent switches at molecular dimensions of less than ten nanometers – the equivalent to 10,000 times thinner than a strand of human hair and less than half the size of the leading silicon technology. Comprehensive modeling of the electronic circuits suggests that about a five to ten times improvement in performance compared to silicon circuits is possible.

Graphene

Graphene is pure carbon in the form of a one atomic layer thick sheet. It is an excellent conductor of heat and electricity, and it is also remarkably strong and flexible. Electrons can move in graphene about ten times faster than in commonly used semiconductor materials such as silicon and silicon germanium. Its characteristics offer the possibility to build faster switching transistors than are possible with conventional semiconductors, particularly for applications in the handheld wireless communications business where it will be a more efficient switch than those currently used.Recently in 2013, IBM demonstrated the world’s first graphene based integrated circuit receiver front end for wireless communications. The circuit consisted of a 2-stage amplifier and a down converter operating at 4.3 GHz.

Next Generation Low Power Transistors

In addition to new materials like CNTs, also new architectures and innovative device concepts are required to boost future system performance. Power dissipation is a fundamental challenge for nanoelectronic circuits. A potential alternative to today’s power hungry silicon field effect transistors are so-called steep slope devices. They could operate at much lower voltage and thus dissipate significantly less power.To reduce the energy consumption in electronics, IBM scientists are researching tunnel field effect transistors (TFETs). In this special type of transistors the quantum-mechanical effect of band-to-band tunneling is used to drive the current flow through the transistor. TFETs could achieve a 100-fold power reduction over complementary CMOS transistors, so integrating TFETs with CMOS technology could improve low-power integrated circuits.

III-V semiconductor nanowires which are cylindrical nanostructures measuring only a few millionths of a centimeter in diameter are ideal materials to build TFETs. Just recently IBM has developed a novel method to integrate III-V nanowires and heterostructures directly on standard Si substrates and built the first ever InAs/Si tunnel diodes and TFETs using InAs as source and Si as channel with wrap-around gate as steep slope device for low power consumption applications.

VentureBeat's mission is to be a digital town square for technical decision-makers to gain knowledge about transformative enterprise technology and transact. Learn More